Chemical Mechanical Planarization (CMP) – Công nghệ làm phẳng bề mặt trong chế tạo bán dẫn

CMP trong chuỗi công nghệ bán dẫn hiện đại

Trong các bài trước của series, chúng ta đã lần lượt đi qua Silicon Wafer Production, Wafer Surface Cleaning, Thermal Oxidation, Thin Film Deposition, Lithography, Etching, và Dopant Diffusion → Ion Implantation.

Sau các bước này, bề mặt wafer trở nên phức tạp với nhiều lớp vật liệu và độ gồ ghề cao, gây khó khăn cho các công đoạn lắng đọng và tạo hình tiếp theo.

Trong bối cảnh đó, Chemical Mechanical Planarization (CMP) được phát triển như một kỹ thuật làm phẳng bề mặt toàn wafer, trở thành một bước nền tảng không thể thiếu trong chế tạo thiết bị bán dẫn đa lớp hiện đại

Nhu cầu planarization và giới hạn của deposition truyền thống

CMP ra đời vào cuối những năm 1980 – đầu 1990, khi:

Số lượng lớp kim loại trong thiết bị tăng nhanh

Địa hình bề mặt wafer ngày càng phức tạp

Các kỹ thuật deposition bắt đầu gặp khó khăn trong gap fill và conformality

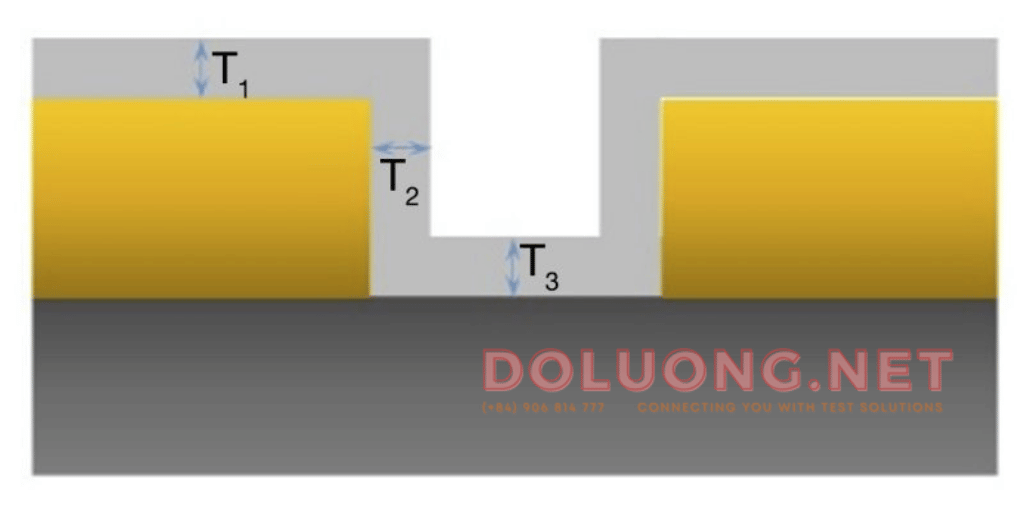

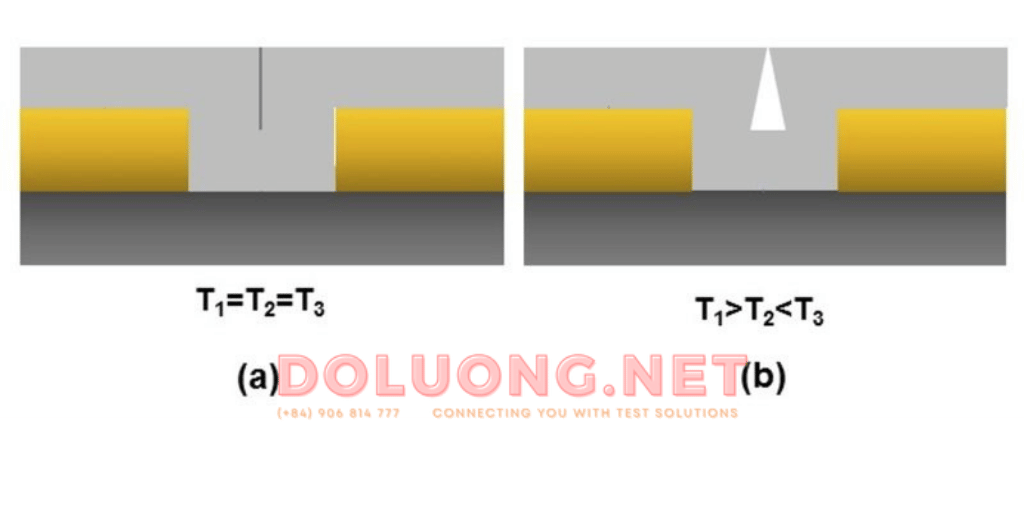

Khái niệm conformal film coverage được dùng để mô tả khả năng màng mỏng phủ đều cả bề mặt phẳng và thành đứng. Khi màng không conformal, các void trong lớp cách điện có thể hình thành và trở thành điểm yếu điện của thiết bị.

Hình 8-1. Các tham số xác định mức độ phủ conformal của màng mỏng trên bề mặt wafer.

Conformal và non-conformal gap fill

Trong trường hợp lý tưởng, màng phủ có độ dày tương đương trên mọi bề mặt. Tuy nhiên, với địa hình gồ ghề:

Màng conformal kém có thể tạo lỗ rỗng

Các điểm này làm tăng nguy cơ device failure

Giới hạn này là một trong những nguyên nhân thúc đẩy sự chuyển dịch từ giải pháp deposition thuần túy sang CMP-based planarization.

Hình 8-2. So sánh giữa gap fill conformal (8.2a) và non-conformal (8.2b) trong cấu trúc bán dẫn.

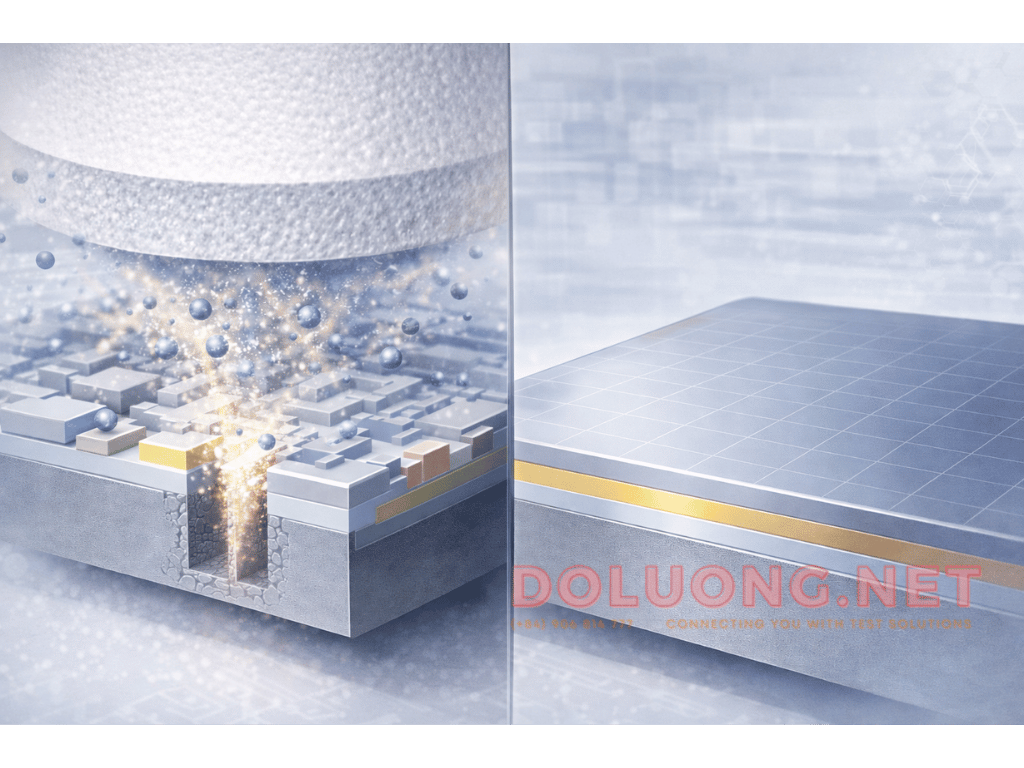

CMP và planarization cấu trúc đa lớp

CMP cho phép chuyển bề mặt wafer từ trạng thái gồ ghề sang phẳng hóa, tạo điều kiện cho tích hợp nhiều lớp kim loại và điện môi.

Theo tài liệu MKS, sự khác biệt giữa cấu trúc không planarized và đã planarized bằng CMP trở nên đặc biệt rõ ràng trong các thiết bị đa lớp phức tạp.

Hình 8-3. So sánh cấu trúc đa lớp kim loại không planarized (8.3a) và đã planarized (8.3b) bằng CMP.

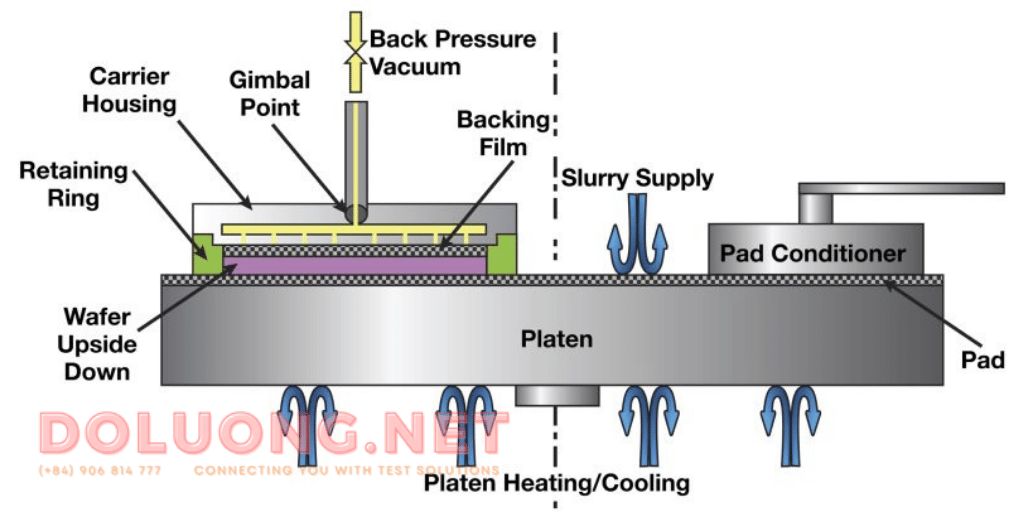

Nguyên lý và cấu trúc hệ thống CMP

CMP là sự kết hợp của:

Tác động cơ học (pad + hạt mài)

Tác động hóa học (slurry chứa chất phản ứng)

Một hệ thống CMP điển hình gồm:

Platen quay với polishing pad

Wafer carrier ép wafer xuống pad bằng áp suất xác định

Slurry được cấp liên tục

Kiểm soát nhiệt độ tại giao diện pad/wafer

Các điểm cao trên bề mặt chịu áp lực lớn hơn, dẫn đến tốc độ loại bỏ vật liệu cao hơn, từ đó tạo ra hiệu ứng planarization.

Hình 8-4. Sơ đồ nguyên lý và các thành phần chính của hệ thống CMP.

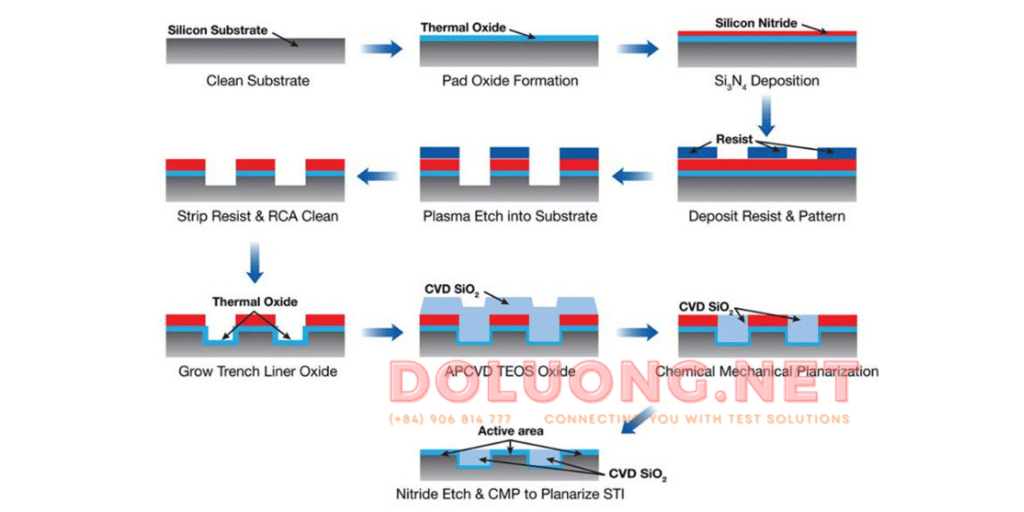

CMP trong Shallow Trench Isolation (STI)

CMP đóng vai trò then chốt trong STI, một công nghệ cách ly đã thay thế LOCOS do yêu cầu về thermal budget và khả năng scaling.

Trong quy trình STI:

Các trench được khắc và lấp đầy bằng oxide

CMP được sử dụng để làm phẳng oxide đến mức nitride

Sau đó tiếp tục planarization các lớp tiếp theo

STI là một trong những yếu tố cho phép thiết bị bán dẫn đạt kích thước nanomet.

Hình 8-5. Quy trình Shallow Trench Isolation (STI) với các bước planarization bằng CMP.

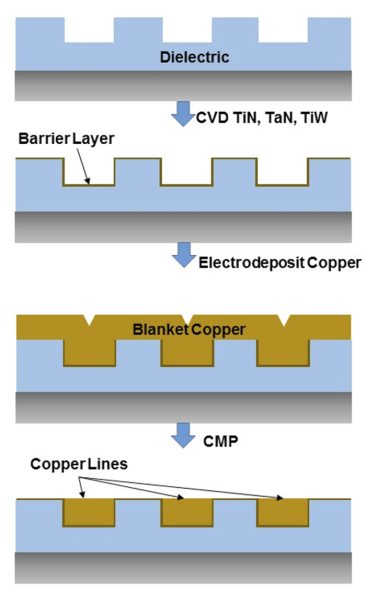

CMP trong Damascene và Dual Damascene

Việc chuyển từ dây nhôm sang dây đồng (Cu) giúp giảm RC delay nhưng đặt ra thách thức lớn:

Đồng không thể khắc bằng dry etch thông thường

Sản phẩm halide của Cu không bay hơi

Giải pháp là Damascene process, trong đó:

Pattern được khắc vào dielectric

Lắng đọng barrier + seed layer

Điện hóa Cu

CMP loại bỏ Cu dư, chỉ để lại Cu trong rãnh

CMP vì thế trở thành công nghệ trung tâm của interconnect đồng.

Hình 8-6. Quy trình Damascene cơ bản sử dụng CMP để tạo dây dẫn đồng.

Từ planarization đến Inspection & Yield

Sau CMP, wafer đạt trạng thái bề mặt phẳng và sẵn sàng cho tích hợp tiếp theo. Tuy nhiên, planarization chỉ thực sự có ý nghĩa khi:

Độ đồng đều được kiểm soát

Khuyết tật được phát hiện sớm

Yield được theo dõi và tối ưu

Recent Posts

- Tất tần tật những điều cần biết về Fiber

- Vì sao Việt Nam bắt đầu từ 32nm – và chip 3nm thực sự dùng để làm gì?

- Newport 1938-R/2938-R vs 1940-R/2940-R – So sánh benchtop Optical Power & Energy Meter và cách chọn đúng hệ đo (detector + phụ kiện) theo ứng dụng

- Chemical Mechanical Planarization (CMP) – Công nghệ làm phẳng bề mặt trong chế tạo bán dẫn

- Dopant Diffusion và Ion Implantation – Kiểm soát tính chất điện trong chế tạo bán dẫn