Dopant Diffusion và Ion Implantation – Kiểm soát tính chất điện trong chế tạo bán dẫn

Vị trí của doping trong chuỗi quy trình bán dẫn

Trong các bài trước của series, chúng ta đã lần lượt đi qua Silicon Wafer Production, Wafer Surface Cleaning, Thermal Oxidation, Thin Film Deposition, Lithography và Etching.

Sau khi hình dạng hình học của linh kiện được xác định thông qua lithography và etching, bước tiếp theo mang tính quyết định đến đặc tính điện của thiết bị bán dẫn chính là đưa tạp chất (dopant) vào silicon.

Hai kỹ thuật cốt lõi được sử dụng trong sản xuất hiện đại là Dopant Diffusion và Ion Implantation, mỗi phương pháp có cơ chế vật lý, mức độ kiểm soát và vai trò khác nhau trong quy trình chế tạo.

Dopant Diffusion – Khuếch tán tạp chất trong silicon

Dopant diffusion là quá trình chuyển động của các nguyên tử tạp chất trong mạng tinh thể silicon ở nhiệt độ cao, với xu hướng làm “làm mượt” các vùng có nồng độ tạp chất cao.

Theo tài liệu MKS, động lực của quá trình khuếch tán chính là gradient nồng độ tạp chất (dC/dx) và hành vi khuếch tán này có thể được mô tả bằng định luật khuếch tán thứ nhất và thứ hai của Fick.

Quá trình khuếch tán thường được thực hiện trong lò ống gia nhiệt kiểu hot-wall, có cấu hình tương tự như các lò oxy hóa nhiệt đã được đề cập trong bài Thermal Oxidation. Nhiệt độ và thời gian xử lý là hai tham số then chốt quyết định độ sâu junction và phân bố nồng độ dopant trong wafer.

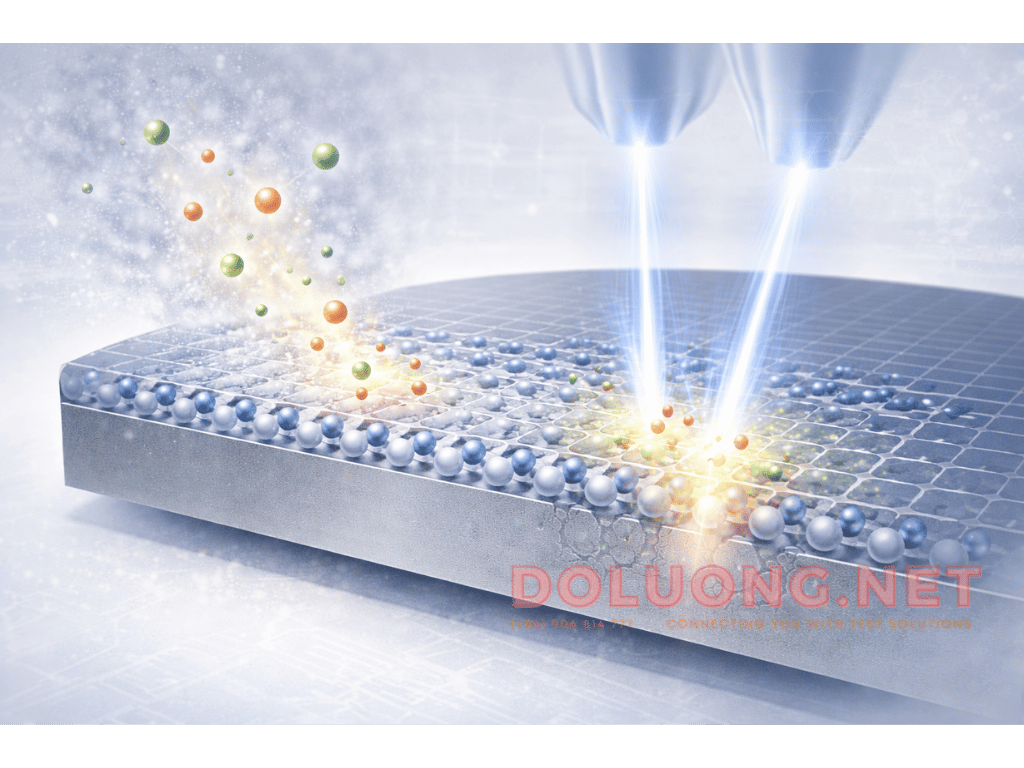

Hình 7.1. Sự khuếch tán của nguyên tử tạp chất trong mạng tinh thể silicon dưới tác động của nhiệt độ cao.

Đặc điểm và giới hạn của Dopant Diffusion

Dopant diffusion có ưu điểm là:

Cơ chế vật lý đơn giản

Phù hợp với các công đoạn nhiệt truyền thống

Dễ áp dụng trong các quy trình bán dẫn thế hệ đầu

Tuy nhiên, khi kích thước linh kiện tiếp tục thu nhỏ, phương pháp khuếch tán bộc lộ nhiều hạn chế:

Khó kiểm soát chính xác profile theo chiều sâu

Phân bố dopant mang tính đẳng hướng

Không phù hợp cho các junction nông và cấu trúc mật độ cao

Những giới hạn này là lý do Ion Implantation trở thành phương pháp doping chủ đạo trong sản xuất bán dẫn hiện đại.

Ion Implantation – Cấy ion với độ chính xác cao

Ion implantation là phương pháp đưa tạp chất vào silicon bằng cách gia tốc ion năng lượng cao và bắn trực tiếp vào bề mặt wafer.

Theo tài liệu MKS, quy trình này cho phép kiểm soát chính xác độ sâu xâm nhập của dopant thông qua năng lượng ion và góc chiếu.

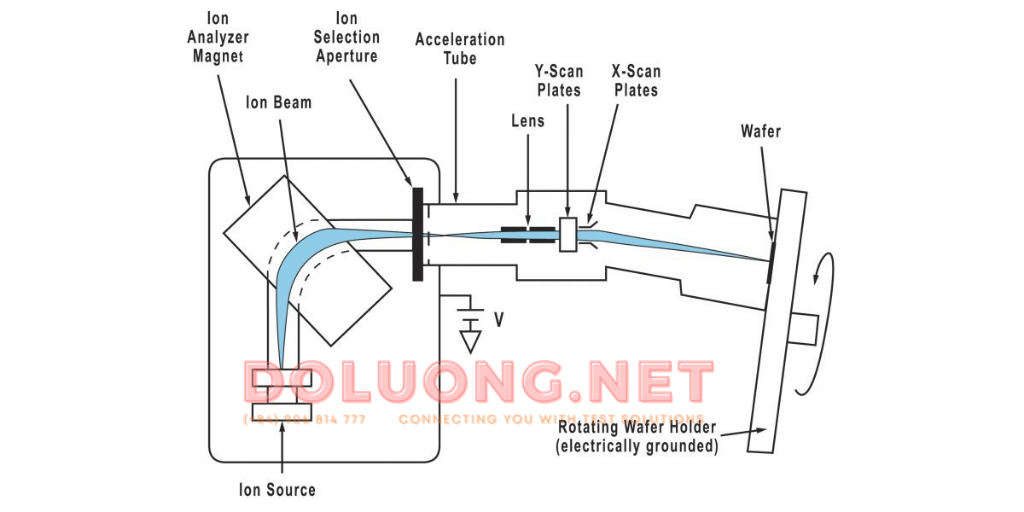

Trong hệ thống cấy ion, các nguyên tử dopant được:

Ion hóa trong nguồn plasma (RF hoặc microwave)

Tách chọn theo tỷ lệ khối lượng/điện tích trong bộ phân tích từ

Gia tốc đến năng lượng từ sub-keV đến MeV

Dẫn hướng và quét đều lên bề mặt wafer trong môi trường chân không cao

Hình 7.2. Cấu trúc và các thành phần chính của hệ thống ion implantation trong chế tạo bán dẫn.

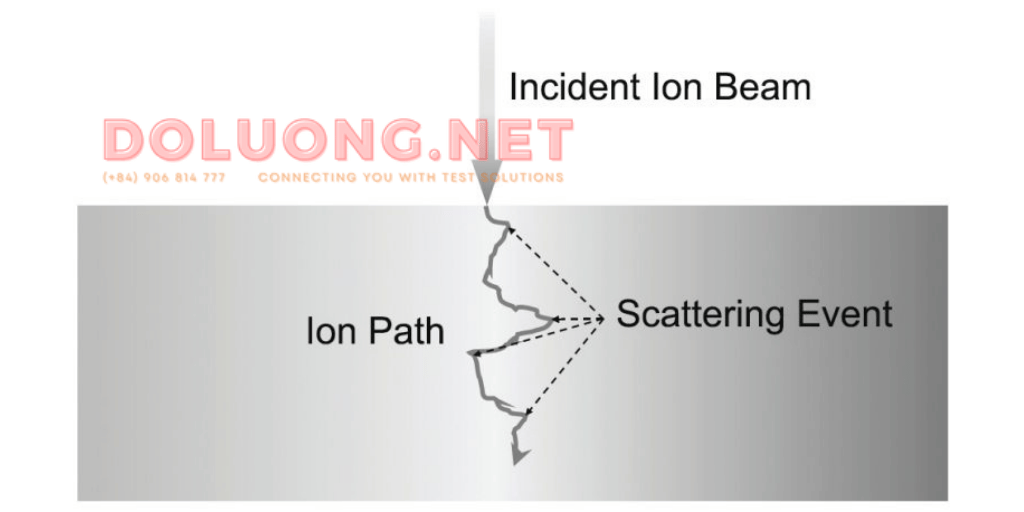

Đường đi ion và profile nồng độ dopant

Ion không di chuyển theo quỹ đạo thẳng trong silicon mà trải qua quá trình tán xạ va chạm với các nguyên tử nền, tạo ra quỹ đạo dạng “drunkard’s walk”.

Hệ quả của hiện tượng này là phân bố nồng độ dopant theo chiều sâu có dạng Gaussian, đặc trưng bởi độ sâu trung bình và độ rộng phân bố.

Sau quá trình cấy ion, các nguyên tử dopant có thể nằm ở các vị trí không thay thế trong mạng tinh thể, đồng thời gây hư hại cấu trúc tinh thể silicon. Vì vậy, quá trình annealing sau cấy là bắt buộc để:

Kích hoạt dopant

Sửa chữa hư hại mạng tinh thể

Điều chỉnh lại profile nồng độ

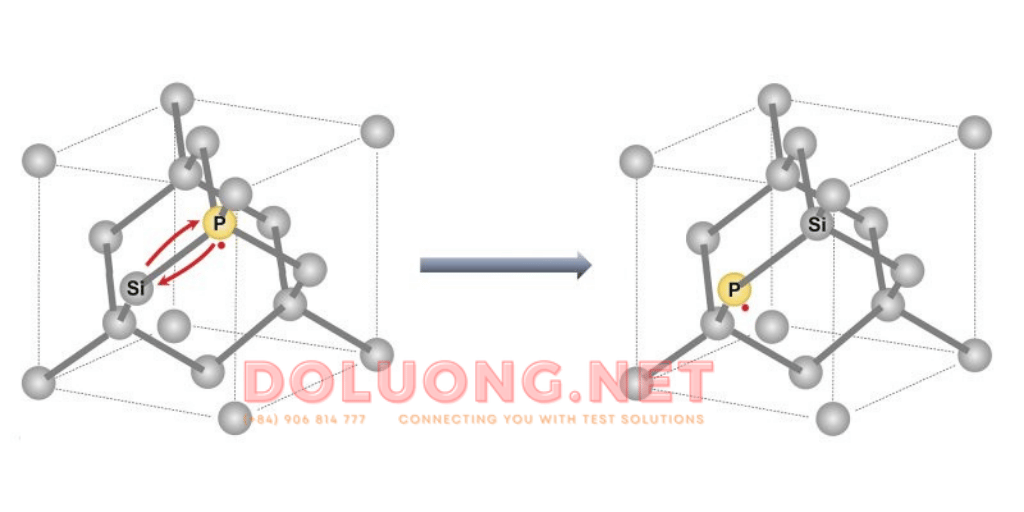

Hình 3. Quỹ đạo xâm nhập của ion trong silicon và phân bố nồng độ dopant theo chiều sâu sau cấy ion.

So sánh vai trò Dopant Diffusion và Ion Implantation

Trong sản xuất bán dẫn hiện đại:

Dopant diffusion thường được sử dụng trong các bước nhiệt đặc thù hoặc công nghệ truyền thống

Ion implantation là phương pháp chủ đạo cho:

n-well / p-well

source/drain

kiểm soát chính xác junction nông

Hai phương pháp này không loại trừ nhau mà bổ sung trong chuỗi thermal processing và electrical property engineering của thiết bị bán dẫn.

Liên hệ giải pháp của MKS trong doping process

Theo tài liệu MKS:

MKS không trực tiếp sản xuất thiết bị cấy ion hay lò khuếch tán, nhưng đóng vai trò OEM supplier cho các hệ thống thermal processing

Các giải pháp của MKS liên quan đến:

Điều khiển và đo áp suất chân không

Mass Flow Controller cho khí công nghệ

Remote plasma cho làm sạch nguồn ion và beamline

Những hệ thống này là hạ tầng không thể thiếu để đảm bảo độ ổn định và độ lặp của quá trình doping trong fab.

Sau khi hoàn tất các bước đưa tạp chất và kiểm soát đặc tính điện của silicon, wafer bước sang giai đoạn làm phẳng bề mặt để chuẩn bị cho các lớp tích hợp tiếp theo.

Bài viết tiếp theo của series sẽ tập trung vào Chemical Mechanical Planarization (CMP) – công nghệ then chốt cho tích hợp đa lớp và cấu trúc bán dẫn mật độ cao.

Recent Posts

- Tất tần tật những điều cần biết về Fiber

- Vì sao Việt Nam bắt đầu từ 32nm – và chip 3nm thực sự dùng để làm gì?

- Newport 1938-R/2938-R vs 1940-R/2940-R – So sánh benchtop Optical Power & Energy Meter và cách chọn đúng hệ đo (detector + phụ kiện) theo ứng dụng

- Chemical Mechanical Planarization (CMP) – Công nghệ làm phẳng bề mặt trong chế tạo bán dẫn

- Dopant Diffusion và Ion Implantation – Kiểm soát tính chất điện trong chế tạo bán dẫn