Wafer Surface Cleaning – Nền tảng kiểm soát bề mặt và yield trong chế tạo bán dẫn

Vai trò của wafer surface cleaning trong sản xuất bán dẫn hiện đại

Trong chuỗi công nghệ chế tạo thiết bị bán dẫn, wafer surface cleaning không còn được xem là một bước chuẩn bị mang tính phụ trợ, mà đã trở thành một trụ cột then chốt quyết định chất lượng và yield của linh kiện. Như đã phân tích trong bài viết về nền tảng vật liệu và vai trò của silicon wafer trong chuỗi sản xuất bán dẫn, mọi công đoạn phía sau đều được xây dựng trên chính bề mặt wafer, nơi các sai lệch dù rất nhỏ cũng có thể bị khuếch đại qua nhiều bước xử lý tiếp theo.

Sự gia tăng số lượng các bước etching, deposition, cùng với việc ứng dụng vật liệu mới và cấu trúc 2.5D/3D, khiến yêu cầu đối với trạng thái bề mặt wafer ngày càng khắt khe. Trước khi wafer đi vào bất kỳ công đoạn xử lý nào trong fab, bề mặt của nó cần được làm sạch để loại bỏ hạt bụi, tạp nhiễm hữu cơ, tạp nhiễm vô cơ, kim loại, cũng như lớp oxide tự nhiên hình thành khi tiếp xúc với không khí.

Trong thực tế sản xuất bán dẫn hiện đại, các bước làm sạch wafer có thể chiếm tới 30–40% tổng số công đoạn, phản ánh vai trò đặc biệt của kiểm soát bề mặt không chỉ đối với hiệu năng thiết bị, mà còn đối với độ ổn định quy trình và độ tin cậy dài hạn của linh kiện bán dẫn.

Các dạng tạp nhiễm trên bề mặt wafer silicon

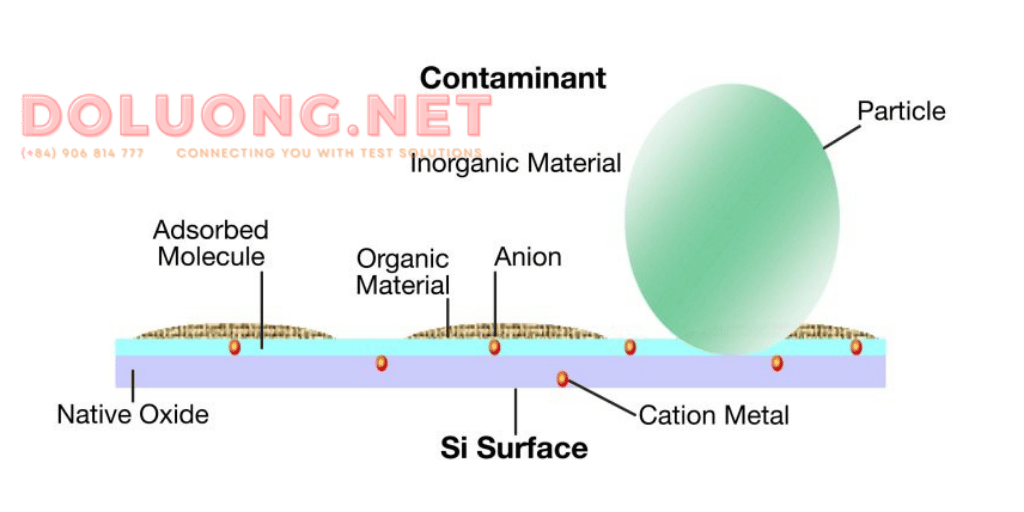

Bề mặt wafer silicon trước khi đưa vào quy trình chế tạo có thể tồn tại nhiều dạng tạp nhiễm khác nhau, bao gồm:

Particle contamination: các hạt rời hoặc cụm hạt có nguồn gốc từ không khí, thiết bị fab, hóa chất, đường ống cấp khí hoặc thao tác wafer.

Metallic contamination: kim loại kiềm và kim loại nặng có khả năng khuếch tán nhanh trong mạng tinh thể silicon, gây suy giảm nghiêm trọng đặc tính điện.

Chemical contamination: các hợp chất hữu cơ, vô cơ hấp phụ trên bề mặt wafer.

Native oxide: lớp oxide mỏng hình thành tự nhiên do silicon phản ứng với oxy và hơi ẩm trong môi trường.

Mỗi loại tạp nhiễm đều có thể dẫn đến các vấn đề như lỗi pattern, suy giảm độ bền lớp oxide cổng, dịch chuyển điện áp ngưỡng (Vth), tăng dòng rò của tiếp giáp PN hoặc giảm tuổi thọ linh kiện. Khi kích thước đặc trưng của thiết bị tiếp tục thu nhỏ, ngay cả các hạt có kích thước nanomet cũng có thể trở thành killer defects.

Hình 2.1 – Các dạng tạp nhiễm trên bề mặt wafer silicon

Mục tiêu và nguyên lý của wafer surface cleaning

Mục tiêu của wafer surface cleaning không chỉ dừng lại ở việc “làm sạch”, mà là tạo ra một bề mặt silicon được kiểm soát chặt chẽ về mặt hóa học và điện, sẵn sàng cho bước xử lý tiếp theo. Một khái niệm quan trọng gắn liền với làm sạch là surface activation, tức điều kiện hóa bề mặt để đảm bảo độ bám dính tốt của các lớp màng lắng đọng, qua đó nâng cao chất lượng die và yield.

Trong môi trường sản xuất thực tế, hiệu quả của quá trình làm sạch phụ thuộc mạnh vào khả năng kiểm soát chính xác lưu lượng hóa chất, áp suất, nhiệt độ và điều kiện môi trường. Đây cũng là lý do các hệ thống kiểm soát quá trình (process control) đóng vai trò then chốt trong wafer surface cleaning hiện đại.

Các phương pháp làm sạch ướt (wet cleaning) kinh điển

Trong front-end-of-line (FEOL), các phương pháp làm sạch ướt vẫn là nền tảng của quy trình. Nổi bật nhất là RCA cleaning, được phát triển từ những năm 1970 và đến nay vẫn được sử dụng rộng rãi trong ngành bán dẫn.

RCA cleaning là chuỗi xử lý kết hợp gồm:

SC-1 (APM): loại bỏ các hạt nhỏ và tạp nhiễm hữu cơ.

SC-2 (HPM): loại bỏ tạp nhiễm kim loại.

Dung dịch HF loãng hoặc BOE: loại bỏ lớp oxide tự nhiên, tạo bề mặt silicon kết thúc bằng hydro (H-terminated).

Chuỗi xử lý này tạo ra một bề mặt wafer sạch, ổn định và có thể lặp lại, sẵn sàng cho các bước như thermal oxidation hoặc thin film deposition.

Trong các hệ thống làm sạch ướt công nghiệp, việc duy trì tỷ lệ pha trộn hóa chất ổn định và điều kiện xử lý chính xác là yếu tố quyết định. Các giải pháp Mass Flow Controller cho semiconductor, Baratron® capacitance manometer và hệ thống process automation của MKS thường được tích hợp nhằm kiểm soát chặt chẽ lưu lượng, áp suất và khả năng lặp lại của quá trình, từ đó giảm biến thiên và cải thiện yield.

Hình 2.2 – Hydrogen termination trên bề mặt Si(100) & Si(111)

Thách thức mới và xu hướng làm sạch wafer hiện đại

Khi công nghệ bán dẫn tiến tới các node nhỏ hơn và cấu trúc phức tạp hơn, các phương pháp làm sạch truyền thống ngày càng gặp giới hạn về an toàn hóa chất và khả năng kiểm soát ở cấp độ nguyên tử. Điều này thúc đẩy sự phát triển của các kỹ thuật dry cleaning, remote plasma và ozone hòa tan trong nước DI (DIO₃).

Các phương pháp này giúp:

Giảm sử dụng hóa chất mạnh

Hạn chế rủi ro an toàn

Nâng cao khả năng kiểm soát bề mặt wafer

Trong bối cảnh đó, các hệ thống microwave generator, remote plasma source và dissolved ozone delivery của MKS được phát triển để hỗ trợ các quy trình làm sạch tiên tiến, đặc biệt phù hợp với yêu cầu của các dây chuyền bán dẫn hiện đại và advanced packaging.

Wafer surface cleaning trong triết lý “Surround the Wafer®”

Wafer surface cleaning không tồn tại như một công đoạn độc lập, mà là mắt xích kết nối trực tiếp giữa vật liệu wafer và các bước xử lý quan trọng tiếp theo như thermal oxidation, deposition hay lithography. Một bề mặt wafer không được làm sạch và điều kiện hóa đúng mức có thể phá hủy toàn bộ lợi thế đạt được từ wafer chất lượng cao và thiết bị xử lý tiên tiến.

Theo triết lý “Surround the Wafer®”, mọi yếu tố xung quanh wafer – từ khí, hóa chất, áp suất, năng lượng plasma đến môi trường xử lý – đều cần được kiểm soát đồng bộ. Trong chuỗi giá trị này, các giải pháp đo lường và kiểm soát quá trình của MKS đóng vai trò hỗ trợ then chốt, giúp đảm bảo chất lượng bề mặt wafer, độ ổn định quy trình và yield của thiết bị bán dẫn.

Kết luận

Trong sản xuất bán dẫn hiện đại, wafer surface cleaning đã chuyển từ một bước chuẩn bị sang một trụ cột cốt lõi của kiểm soát chất lượng và yield. Việc hiểu rõ bản chất của tạp nhiễm, cơ chế làm sạch và mối liên hệ với các công đoạn tiếp theo là nền tảng để tiếp cận sâu hơn các hướng nghiên cứu và phát triển trong chế tạo thiết bị bán dẫn.

Từ một bề mặt wafer đã được làm sạch và điều kiện hóa chính xác, bước tiếp theo trong chuỗi chế tạo bán dẫn là quá trình hình thành các lớp oxide được kiểm soát chặt chẽ – chủ đề của Thermal Oxidation, nơi ranh giới giữa vật liệu và thiết bị bắt đầu được định hình.

Recent Posts

- Tất tần tật những điều cần biết về Fiber

- Vì sao Việt Nam bắt đầu từ 32nm – và chip 3nm thực sự dùng để làm gì?

- Newport 1938-R/2938-R vs 1940-R/2940-R – So sánh benchtop Optical Power & Energy Meter và cách chọn đúng hệ đo (detector + phụ kiện) theo ứng dụng

- Chemical Mechanical Planarization (CMP) – Công nghệ làm phẳng bề mặt trong chế tạo bán dẫn

- Dopant Diffusion và Ion Implantation – Kiểm soát tính chất điện trong chế tạo bán dẫn

5 thoughts on “Wafer Surface Cleaning – Nền tảng kiểm soát bề mặt và yield trong chế tạo bán dẫn”

Pingback: Thermal Oxidation – Quá trình hình thành lớp oxide nền tảng trong chế tạo bán dẫn - Thiết bị đo lường | Trang chủ

Pingback: Thin Film Deposition – Công nghệ lắng đọng màng mỏng trong chế tạo bán dẫn hiện đại - Thiết bị đo lường | Trang chủ

Pingback: Etching – Công nghệ khắc tạo hình trong chế tạo bán dẫn hiện đại - Thiết bị đo lường | Trang chủ

Pingback: Lithography – Công nghệ tạo hình vi cấu trúc trong chế tạo bán dẫn - Thiết bị đo lường | Trang chủ

Pingback: Chemical Mechanical Planarization (CMP) – Công nghệ làm phẳng bề mặt trong chế tạo bán dẫn - Thiết bị đo lường | Trang chủ